# 256K x 16 Bit CMOS Video RAM

#### **FEATURES**

- Dual port Architecture 256K x 16 bits RAM port 512 x 16 bits SAM port

- · Performance range :

| Parameter            | Speed      | -5    | -6        | -7   |  |

|----------------------|------------|-------|-----------|------|--|

| RAM access time (tr  | AC)        | 50ns  | 60ns      | 70ns |  |

| RAM access time (to  | AC)        | 15ns  | 15ns      | 20ns |  |

| RAM cycle time (tRC) | 85ns       | 130ns |           |      |  |

| RAM page cycle (the  | c)         | 20ns  | 28ns      |      |  |

| SAM access time (ts  | CA)        | 15ns  | 15ns 15ns |      |  |

| SAM cycle time (tsco | c)         | 18ns  | 18ns      | 20ns |  |

| RAM active corrent   | KM4216C258 | 130m  | 120m      | 110m |  |

| SAM active current   | KM4216C258 | 40mA  | 50mA      | 45mA |  |

- · Fast Page Mode with Extended Data Out

- · RAM Read, Write, Read-Modify-Write

- · Serial Read (SR)

- · Read / Real time read transfer (RT, RRT)

- · Split Read Transfer with Stop Operation (SRT)

- 2 CAS Byte / Word Read / Write Operation

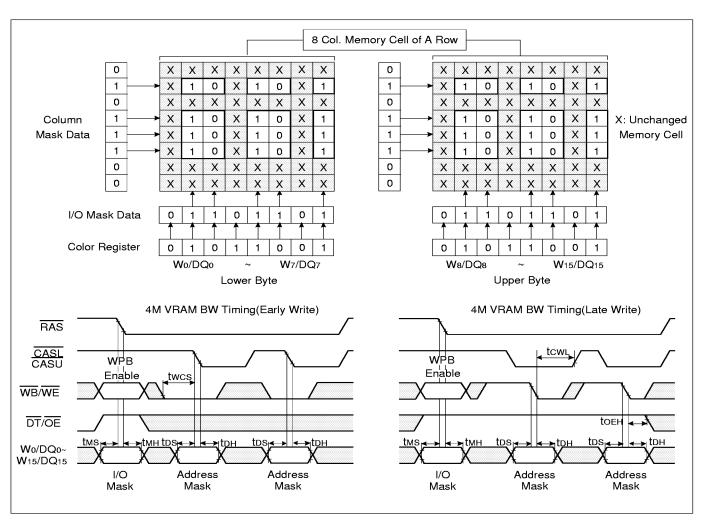

- 8 Column Block Write (BW) and Write-per-Bit with Masking Operation (New and Old Mask)

- · CAS-before-RAS, RAS-only and Hidden Refresh

- · Common Data I/O Using three state RAM Output Control

- · All Inputs and Outputs TTL Compatible

- · Refresh: 512 Cycle/8ms

- Single +5V  $\pm$  10% Supply Voltage

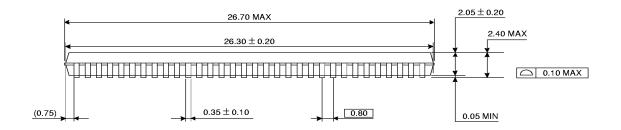

- · Plastic 64-Pin 525mil SSOP (0.8mm pin pitch)

### **GENERAL DESCRIPTION**

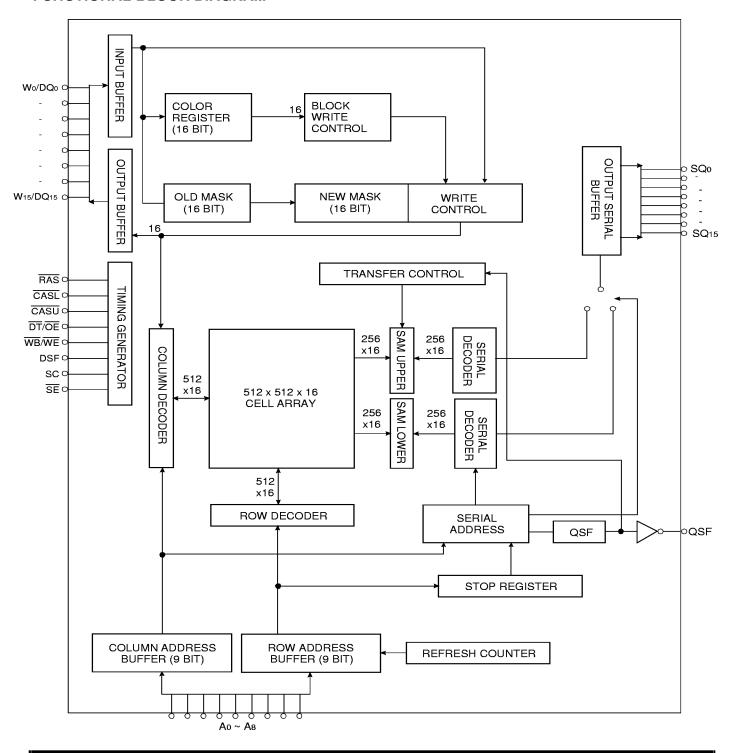

The Samsung KM4216C258 is a CMOS 256K x 16 bit Dual Port DRAM. It consists of a 256K x 16 dynamic random access memory (RAM) port and 512 x 16 static serial access memory (SAM) port. The RAM and SRAM port operate asynchronously except during data transfer between the ports.

The RAM array consists of 512 bit rows of 8192 bits. It operates like a conventional 256K x 16 CMOS DRAM. The RAM port has a write per bit mask capability. Data may be written with New and Old Mask. The RAM port has a Fast Page mode access with Extended Data out, Byte/Word write operation and Block Write capabilities.

The SAM port consists of sixteen 512 bit high speed shift registers that are connected to the RAM array through a 8192 bit data transfer gate. The SAM port has serial read capability.

Data may be internally transferred from the RAM to SAM port using read, and programmable (Stop Register) Split Transfers. Refresh is accomplished by familiar DRAM refresh modes. The KM4216C258 supports RAS-only, Hidden, and CAS-before-RAS refresh for the RAM port. The SAM port does not require refresh.

All inputs and I/O s are TTL level compatible. All address lines and data inputs are latched on chip to simplify system design. The outputs are unlatched to allow greater system flexibility.

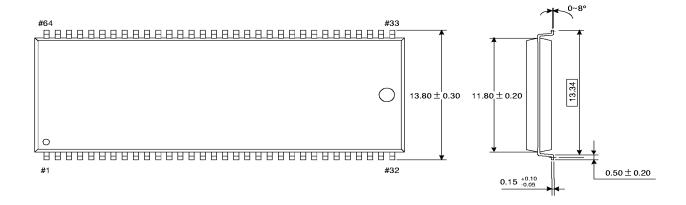

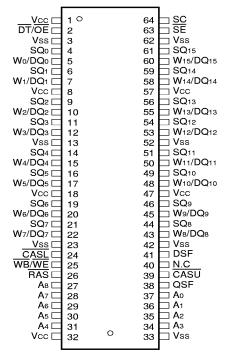

## PIN CONFIGURATION (TOP VIEWS)

### 64-Pin 525 mil SSOP

# **PIN DESCRIPTION**

| SYMBOL         | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |

|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAS            | IN     | Row address strobe. RAS is used to clock in the 9 row bits for another input signal. The RAM port is placed in standby mode when the RAS control is held "high"                                                                                                                                                                                       |

| CASL, CASU     | IN     | Column address strobe. CASL, CASU are used to clock in the 9 column address bits as a strobe forthe DSF inputs and used to Byte/Word Read, Write Operation.                                                                                                                                                                                           |

| Address        | IN     | Address inputs for the DRAM operation, these inputs are multiplexed and clocked by RAS and CAS to select one 16-bit word out of the 262,144 available. 9 row address bits are latched on the falling edge of the row address strobe (RAS) and the following 9 column address bits are latched on the falling edge of the column address strobe (CAS). |

| WB/WE          | IN     | The WB/WE input is a multi-function pin. When WB/WE is "High" at the falling edge of RAS, during RAM port operation, it is used to write data into the memory array in the same as a standard DRAM. When WB/WE is "Low" at the falling edge of RAS, during RAM port operation, the W-P-B function is enabled.                                         |

| DT/OE          | IN     | The DT/OE input is also a multi-function pin. Enables an internal Transfer operation at the falling edge of RAS when Transfer is enable.                                                                                                                                                                                                              |

| DSF            | IN     | DSF is used to indicate which special functions (BW, FW, Split Transfer, etc.) are used for a particular access cycle.                                                                                                                                                                                                                                |

| <b>W</b> i/DQi | IN/OUT | Data I/O for DRAM access. These pins act as inputs for Mask and register load cycles, DQ Mask and Column Mask for BW.                                                                                                                                                                                                                                 |

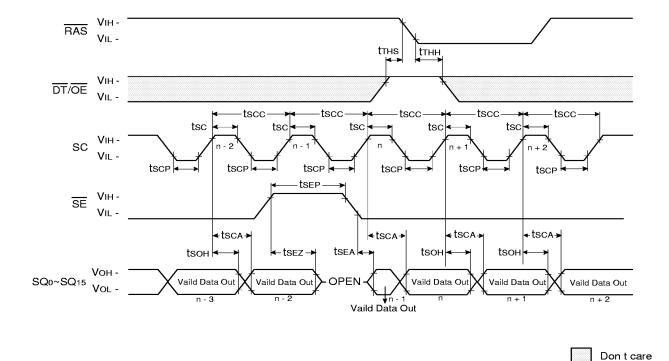

| SC             | IN     | Clock input to the serial address counter and data latch for the SAM register.                                                                                                                                                                                                                                                                        |

| SQi            | OUT    | Serial output pin for serial read.(Serial write is not supported)                                                                                                                                                                                                                                                                                     |

| QSF            | OUT    | QSF indicates which half of the SAM is being accessed. Low if address is 0~255, High if address is 256~511.                                                                                                                                                                                                                                           |

| SE             | IN     | In a serial read cycle, SE is used as an output control. When SE is "High", serial access is disabled, however, the serial address pointer is still incremented while SC is clocked.                                                                                                                                                                  |

| Vcc            | SUPPLY | Power supply                                                                                                                                                                                                                                                                                                                                          |

| Vss            | SUPPLY | Ground                                                                                                                                                                                                                                                                                                                                                |

### **FUNCTIONAL BLOCK DIAGRAM**

Rev. 0.11 (Aug. 1998)

### **FUNCTION TRUTH TABLE**

| Mnemonic           |     | RAS ~ |    | CAS | Add          | ress            | DC   | i Input | Reg            | ister           | Function |                                        |

|--------------------|-----|-------|----|-----|--------------|-----------------|------|---------|----------------|-----------------|----------|----------------------------------------|

| Code               | CAS | DT/OE | WE | DSF | DSF          | RAS             | CAS  | RAS     | CAS/WE         | Mask            | Color    | Function                               |

| CBRS<br>(Note 1,3) | 0   | х     | 0  | 1   | -            | Stop<br>(Note4) | -    | ×       | -              | -               | -        | CBR Refresh/Stop<br>(No reset)         |

| CBRN<br>(Note 1)   | 0   | х     | 1  | 1   | -            | Х               | -    | х       | -              | -               | -        | CBR Refresh<br>(No reset)              |

| CBRR<br>(Note 1)   | 0   | х     | х  | 0   | -            | Х               | -    | х       | -              | -               | -        | CBR Refresh<br>(Option reset)          |

| ROR                | 1   | 1     | Х  | 0   | -            | Row             | -    | Х       | -              | -               | -        | RAS - only Refresh                     |

| RT                 | 1   | 0     | 1  | 0   | Х            | Row             | Тар  | Х       | х              | -               | -        | Read Transfer                          |

| SRT                | 1   | 0     | 1  | 1   | Х            | Row             | Тар  | Х       | х              | -               | -        | Split Read Transfer                    |

| RWM                | 1   | 1     | 0  | 0   | 0            | Row             | Col. | WMi     | Data           | Use             | -        | Masked Write<br>(New / Old Mask)       |

| в <b>w</b> м       | 1   | 1     | 0  | 0   | 1            | Row             | Col. | WMi     | Column<br>Mask | Use             | Use      | Masked Block Write<br>(New / Old Mask) |

| RW                 | 1   | 1     | 1  | 0   | 0<br>(Note6) | Row             | Col. | ×       | Data           | -               | -        | Read or Write                          |

| BW                 | 1   | 1     | 1  | 0   | 1            | Row             | Col. | ×       | Column<br>Mask | -               | Use      | Block Write                            |

| LMR<br>(Note 2)    | 1   | 1     | 1  | 1   | 0            | Row<br>(Note7)  | х    | ×       | WMi            | Load<br>(Note5) | -        | Load(Old) Mask<br>Register set Cycle   |

| LCR                | 1   | 1     | 1  | 1   | 1            | Row<br>(Note7)  | ×    | ×       | Color          | -               | Load     | Load Color<br>Register set Cycle       |

$X: Don \ t \ Care, -: Not \ Applicable, Tap: SAM \ Start (Column) \ Address, WMi: Write Mask Data (i=0 ~15) \ \overline{RAS}$  only refresh does not reset Stop or LMR functions.

### Notes:

- (1) CBRS, CBRN and CBRR all perform CAS-before-RAS refresh cycles. CBRR is used to reset all options and either CBRS or CBRN is used to continue to refresh the RAM without clearing any of the options.

- (2) After LMR cycle, RWM and BWM use old mask. (Use CBRR reset to new mask, use CBRS or CBRN to perform CAS-before-RAS refresh while using Old mask)

- (3) After CBRS cycle, SRT use Stop Register as a boundary address.

- (4) Stop defines the column on which shift out moves to the other half of the SAM.

- (5) After LMR, Mask Register is only changed by the another LMR or CBRR cycle.

- (6) In the case of read cycle, DSF is don t care

- (7) The Row that is addressed will be refreshed, but a Row address is not required.

# **ABSOLUTE MAXIMUM RATINGS\***

| Item                               | Symbol    | Rating<br>KM4216C256 | Unit |

|------------------------------------|-----------|----------------------|------|

| Voltage on Any Pin Relative to Vss | Vin, Vout | -1 to + 7.0          | V    |

| Voltage on Supply Relative to Vss  | Vcc       | -1 to + 7.0          | V    |

| Storage Temperature                | Tstg      | -55 to +150          | °C   |

| Power dissipation                  | Po        | 1                    | w    |

| Short circuit output current       | los       | 50                   | mA   |

Permanent device damage may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS (Voltage Reference to Vss, TA = 0 to 70°C)

| Item               | Symbol |       | Unit |        |     |

|--------------------|--------|-------|------|--------|-----|

| Item               | Symbol | Min   | Тур  | Max    | Ont |

| Supply Voltage     | Vcc    | 4.5   | 5.0  | 5.5    | V   |

| Ground             | Vss    | О     | О    | О      | V   |

| Input High Voltage | ViH    | 2.4   | -    | Vcc+1V | V   |

| Input Low Voltage  | VIL    | - 1.0 | -    | 0.8    | V   |

# **INPUT/OUTPUT CURRENT** (Recommended operating conditions unless otherwise noted.)

| ltem                                                                                                     | Symbol | Min | Max | Unit |

|----------------------------------------------------------------------------------------------------------|--------|-----|-----|------|

| Input Leakage Current { Any Input $0 \le VIN \le VCC + 0.5V$ , all other pins not under test = 0 volts.} | lıL    | -10 | 10  | uA   |

| Output Leakage Current (Data out is disabled, 0V ≤ Vouт ≤ Vcc)                                           | loL    | -10 | 10  | uA   |

| Output High Voltage Level<br>(RAM IoH=-2mA, SAM IoH=-2mA)                                                | Vон    | 2.4 | -   | V    |

| Output Low Voltage Level (RAM loL= 2mA, SAM loL= 2mA)                                                    | Vol    | -   | 0.4 | V    |

# CAPACITANCE (Vcc = 5V, f=1MHz, Ta=25 °C)

| Item                                                    | Symbol | Min | Max | Unit |

|---------------------------------------------------------|--------|-----|-----|------|

| Input Capacitance (Ao ~ As)                             | CIN1   | 2   | 6   | pF   |

| Input Capacitance (RAS, CAS, WB/WE, DT/OE, SE, SC, DSF) | CIN2   | 2   | 7   | pF   |

| Input/Output Capacitance (Wo/DQ0 ~ W15/DQ15)            | CDQ    | 2   | 7   | pF   |

| Output Capacitance (SQ0~SQ15, QSF)                      | Csq    | 2   | 7   | pF   |

# DC AND OPERATING CHARACTERISTICS

(Recommended operating conditions unless otherwise noted)

| Parameter (RAM Port)                                                                                        | SAM port   | Symbol | ŀ   | Unit |     |      |

|-------------------------------------------------------------------------------------------------------------|------------|--------|-----|------|-----|------|

| Parameter (NAM Port)                                                                                        | SAW port   | Symbol | -5  | -6   | -7  | Onit |

| Operating Current*1                                                                                         | Standby *2 | Icc1   | 130 | 120  | 110 | mA   |

| (RAS and CAS Cycling @ tsc=min)                                                                             | Active     | Icc1 A | 170 | 160  | 145 | mA   |

| Standby Current                                                                                             | Standby *2 | ICC2   | 10  | 10   | 10  | mA   |

| $(\overline{RAS}, \overline{CAS}, \overline{DT}/\overline{OE}, \overline{WB}/\overline{WE} = VIH, DSF=VIL)$ | Active     | Icc2 A | 55  | 50   | 45  | mA   |

| RAS Only Refresh Current *1                                                                                 | Standby *2 | Іссз   | 130 | 120  | 110 | mA   |

| $(\overline{CAS} = VIH, \overline{RAS} Cycling @ tRC=min)$                                                  | Active     | Іссз А | 170 | 160  | 145 | mA   |

| Extended Fast Page Mode Current *1                                                                          | Standby *2 | ICC4   | 130 | 120  | 110 | mA   |

| (RAS = VIL, CAS Cycling @ tpc=min)                                                                          | Active     | Icc4 A | 170 | 160  | 145 | mA   |

| CAS- Before-RAS Refresh Current *1                                                                          | Standby *2 | ICC5   | 130 | 120  | 110 | mA   |

| (RAS and CAS Cycling @ trc=min)                                                                             | Active     | ICC5 A | 170 | 160  | 145 | mA   |

| Data Transfer Current *1                                                                                    | Standby *2 | Icc6   | 160 | 140  | 130 | mA   |

| (RAS and CAS Cycling @ trc=min)                                                                             | Active     | Icce A | 190 | 180  | 165 | mA   |

| Block Write Cycle Current *1                                                                                | Standby *2 | ICC7   | 130 | 120  | 110 | mA   |

| (RAS and CAS Cycling @ trc=min)                                                                             | Active     | ICC7 A | 170 | 160  | 145 | mA   |

| Color Register Load Current *1                                                                              | Standby *2 | ICC8   | 120 | 110  | 90  | mA   |

| (RAS and CAS Cycling @ tac=min)                                                                             | Active     | Iccs A | 170 | 140  | 125 | mA   |

Note \*1. Real values dependent on output loading and cycle rates. Specified values are obtained with the output open. lcc is specified as average current.

In Icc1, Icc3, Icc6, Icc7, Icc8, address transition should be changed only once while  $\overline{RAS} = VIL$  In Icc4, Address transition should be changed only once while  $\overline{CAS} = VIH$

\*2. SAM standby condition :  $\overline{SE} \ge VIH$ ,  $SC \le VIL$  or  $\ge VIH$

# **CMOS VIDEO RAM**

| AC CHARACTERISTICS | ( 0 °C $\leq$ Ta $\leq$ 70 °C, KM4216C258 : Vcc=5.0V $\pm$ 10%) |

|--------------------|-----------------------------------------------------------------|

|--------------------|-----------------------------------------------------------------|

| Parameter                                   | Symbol | -   | 5*Note13 |     | -6   |     | ·7   | Heit                                     | Notes       |

|---------------------------------------------|--------|-----|----------|-----|------|-----|------|------------------------------------------|-------------|

| Farameter                                   | Symbol | Min | Max      | Min | Max  | Min | Max  | ns n | Notes       |

| Random read or write cycle time             | trc    | 85  |          | 104 |      | 124 |      | ns                                       |             |

| Read-modify-write cycle time                | trwc   | 135 |          | 140 |      | 170 |      | ns                                       |             |

| Hyper page mode cycle time                  | tHPC   | 20  |          | 25  |      | 30  |      | ns                                       | 21          |

|                                             |        | 25  |          | 30  |      | 35  |      | ns                                       | 22          |

| Hyper page read-modify-write cycle time     | thprwc | 66  |          | 70  |      | 74  |      | ns                                       | 21          |

|                                             |        | 72  |          | 76  |      | 81  |      | ns                                       | 22          |

| Access time from RAS                        | trac   |     | 50       |     | 60   |     | 70   | ns                                       | 3,5,11      |

| Access time from CAS                        | tcac   |     | 15       |     | 15   |     | 20   | ns                                       | 3,5,6       |

| Access time from column address             | taa    |     | 25       |     | 30   |     | 35   | ns                                       | 3,11        |

| Access time from CAS Precharge              | tcpa   |     | 30       |     | 35   |     | 40   | ns                                       | 3           |

| CAS to output in Low-Z                      | tcLZ   | 3   |          | 3   |      | 3   |      | ns                                       | 3           |

| Output buffer turn-off delay                | toff   | 3   | 15       | 3   | 15   | 3   | 15   | ns                                       | 7           |

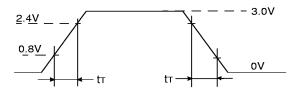

| Transition time (rise and fall)             | tт     | 2   | 50       | 2   | 50   | 2   | 50   |                                          | 2           |

| RAS precharge time                          | trp    | 30  |          | 40  |      | 50  |      | ns                                       |             |

| RAS pulse width                             | tras   | 50  | 10K      | 60  | 10K  | 70  | 10K  | ns                                       |             |

| RAS pulse width (Hyper page cycle)          | trasp  | 50  | 100K     | 60  | 100K | 70  | 100K | ns                                       |             |

| RAS hold time                               | trsh   | 15  |          | 15  |      | 20  |      |                                          |             |

| CAS hold time                               | tcsH   | 45  |          | 45  |      | 55  |      |                                          |             |

| CAS pulse width                             | toas   | 10  | 10K      | 10  | 10K  | 10  | 10K  |                                          | 21          |

| ·                                           |        | 15  | 1        | 15  |      | 15  | 1    | ns                                       | 22          |

| RAS to CAS delay time                       | trcd   | 15  | 35       | 15  | 45   | 15  | 50   | ns                                       | 5           |

| RAS to column addr. delay time              | trad   | 12  | 25       | 12  | 30   | 12  | 35   |                                          | 11          |

| CAS to RAS precharge time                   | tcrp   | 5   |          | 5   |      | 5   |      |                                          |             |

| CAS precharge time (CBR Counter test cycle) | tcpt   | 15  |          | 20  |      | 25  |      | ns                                       |             |

| CAS precharge time (Hyper page cycle)       | tcp    | 6   |          | 10  |      | 10  |      |                                          | 16          |

| Output hold time from CAS                   | tрон   | 3   |          | 3   |      | 3   |      |                                          |             |

| Row addr. set-up time                       | tasr   | 0   |          | 0   |      | 0   |      |                                          |             |

| Row addr. hold time                         | trah   | 8   |          | 10  |      | 10  |      |                                          |             |

| Column addr. set-up time                    | tasc   | 0   |          | 0   |      | 0   |      |                                          | 15          |

| Column addr. hold time                      | tcah   | 8   |          | 10  |      | 12  |      |                                          | 15          |

| Column addr. to RAS lead time               | tral   | 25  |          | 30  |      | 35  |      |                                          |             |

| Read command set-up time                    | trcs   | 0   |          | 0   |      | 0   |      |                                          |             |

| Read command hold referenced to CAS         | trice  | 0   |          | 0   |      | 0   |      |                                          | 9           |

| Read command hold referenced to RAS         | trrh   | 0   |          | 0   |      | 0   |      |                                          | 9           |

| Output buffer turn off delay from WB/WE     | twez   | 3   | 15       | 3   | 15   | 3   | 15   |                                          | 7           |

| Write command pulse width                   | twpz   | 10  |          | 10  | 1.5  | 10  |      |                                          | 7           |

| Write command hold time                     | twch   | 10  |          | 10  |      | 10  |      |                                          | <u> </u>    |

| Write command pulse width                   | twp    | 10  |          | 10  |      | 10  |      | ns                                       |             |

| Write command to RAS lead time              | trwL   | 15  |          | 15  | 1    | 15  |      | ns                                       | <del></del> |

# AC CHARACTERISTICS (Continued)

| Parameter                                    | Symbol |     | 5   |     | -6  |     | .7  | Unit | Notes |

|----------------------------------------------|--------|-----|-----|-----|-----|-----|-----|------|-------|

| Parameter                                    | Symbol | Min | Max | Min | Max | Min | Max | Unit | Notes |

| Write command to CAS lead time               | towL   | 15  |     | 15  |     | 15  |     | ns   | 18    |

| Data set-up time                             | tos    | 0   |     | 0   |     | 0   |     | ns   | 10    |

| Data hold time                               | tон    | 8   |     | 10  |     | 12  |     | ns   | 10    |

| Write command set-up time                    | twcs   | 0   |     | 0   |     | 0   |     | ns   | 8     |

| CAS to WE delay                              | tcwp   | 35  |     | 40  |     | 45  |     | ns   | 8,17  |

| RAS to WE delay                              | trwD   | 80  |     | 85  |     | 95  |     | ns   | 8     |

| Column addr. to WE delay time                | tawd   | 45  |     | 50  |     | 55  |     | ns   | 8     |

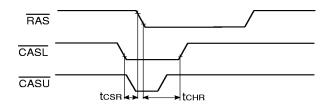

| CAS set-up time (CBR refresh)                | tcsn   | 5   |     | 5   |     | 5   |     | ns   | 19    |

| CAS hold time (CBR refresh)                  | tchr   | 10  |     | 10  |     | 10  |     | ns   | 20    |

| RAS precharge to CAS hold time               | trpc   | 5   |     | 5   |     | 5   |     | ns   |       |

| Access time from output enable               | toea   |     | 15  |     | 15  |     | 20  | ns   |       |

| Output enable to data input delay            | toed   | 10  |     | 15  |     | 15  |     | ns   | 7     |

| Output buffer turn-off delay from OE         | toez   | 3   | 15  | 3   | 15  | 3   | 15  | ns   |       |

| Output enable command hold time              | toeh   | 15  |     | 15  |     | 15  |     | ns   |       |

| Data to CAS delay                            | tozc   | 0   |     | 0   |     | 0   |     | ns   |       |

| Data to output enable delay                  | tozo   | 0   |     | 0   |     | 0   |     | ns   |       |

| Refresh period (512 cycle)                   | tref   |     | 8   |     | 8   |     | 8   | ms   |       |

| WB set-up time                               | twsr   | 0   |     | 0   |     | 0   |     | ns   |       |

| WB hold time                                 | trwn   | 8   |     | 10  |     | 10  |     | ns   |       |

| DSF set-up time referenced to RAS            | trsr   | 0   |     | 0   |     | 0   |     | ns   |       |

| DSF hold time referenced to RAS              | treh   | 8   |     | 10  |     | 10  |     | ns   |       |

| DSF set-up time referenced to CAS            | trsc   | 0   |     | 0   |     | 0   |     | ns   |       |

| DSF hold time referenced to CAS              | tcfH   | 8   |     | 10  |     | 15  |     | ns   |       |

| Write per bit mask data set-up time          | tms    | 0   |     | 0   |     | 0   |     | ns   |       |

| Write per bit mask data hold time            | tмн    | 8   |     | 10  |     | 10  |     | ns   |       |

| DT high set-up time                          | tтнs   | 0   |     | 0   |     | 0   |     | ns   |       |

| DT high hold time                            | tтнн   | 8   |     | 10  |     | 10  |     | ns   |       |

| DT low set-up time                           | tTLS   | 0   |     | 0   |     | 0   |     | ns   |       |

| DT low hold time                             | ttlh   | 8   |     | 10  |     | 10  |     | ns   |       |

| DT low hold referenced to RAS (RRT)          | trth   | 45  |     | 50  |     | 60  |     | ns   |       |

| DT low hold referenced to CAS (RRT)          | tстн   | 15  |     | 15  |     | 20  |     | ns   |       |

| DT low hold refer. to column address (RRT)   | tath   | 20  |     | 20  |     | 25  |     | ns   |       |

| DT precharge time                            | tтр    | 20  |     | 20  |     | 20  |     | ns   |       |

| RAS to first SC delay (Read Transfer)        | trsd   | 50  |     | 60  |     | 70  |     | ns   |       |

| CAS to first SC delay (Read Transfer)        | tcsp   | 20  |     | 25  |     | 30  |     | ns   |       |

| Col. Addr. to first SC delay (Read Transfer) | tasd   | 25  |     | 30  |     | 35  |     | ns   |       |

| Last SC to DT lead time                      | ttsl   | 5   |     | 5   |     | 5   |     | ns   |       |

## KM4216C258

### AC CHARACTERISTICS (Continued)

| Parameter                                 | Combat. |     | -5  |     | 6   |     | 7   | 11                                       | Notes |

|-------------------------------------------|---------|-----|-----|-----|-----|-----|-----|------------------------------------------|-------|

| Parameter                                 | Symbol  | Min | Max | Min | Max | Min | Max | ns n | Notes |

| DT to first SC delay time (Read Transfer) | trsp    | 10  |     | 10  |     | 10  |     | ns                                       |       |

| Last SC to RAS set-up time                | tsrs    | 20  |     | 20  |     | 20  |     | ns                                       |       |

| SC cycle time                             | tscc    | 18  |     | 18  |     | 20  |     | ns                                       | 14    |

| SC pulse width (SC high time)             | tsc     | 5   |     | 5   |     | 7   |     | ns                                       |       |

| SC precharge (SC low time)                | tscp    | 5   |     | 5   |     | 7   |     | ns                                       |       |

| Access time from SC                       | tsca    |     | 15  |     | 15  |     | 17  | ns                                       | 4     |

| Serial output hold time from SC           | tsон    | 3   |     | 3   |     | 5   |     | ns                                       |       |

| Access time from SE                       | tsea    |     | 15  |     | 15  |     | 17  | ns                                       | 4     |

| SE pulse width                            | tse     | 20  |     | 20  |     | 20  |     | ns                                       |       |

| SE precharge time                         | tsep    | 20  |     | 20  |     | 20  |     | ns                                       |       |

| Serial output turn-off from SE            | tsez    | О   | 15  | 0   | 15  | 0   | 15  | ns                                       | 7     |

| Split transfer set-up time                | tsts    | 20  |     | 20  |     | 25  |     | ns                                       |       |

| Split transfer hold time                  | tsтн    | 20  |     | 20  |     | 25  |     | ns                                       |       |

| SC-QSF delay time                         | tsqD    |     | 20  |     | 20  |     | 25  | ns                                       |       |

| DT-QSF delay time                         | tтqd    |     | 20  |     | 20  |     | 25  | ns                                       |       |

| RAS-QSF delay time                        | trqd    |     | 65  |     | 70  |     | 75  | ns                                       |       |

| CAS-QSF delay time                        | tcqp    |     | 35  |     | 35  |     | 35  | ns                                       |       |

| DT to RAS precharge time                  | ttrp    | 40  |     | 40  |     | 50  |     | ns                                       |       |

| DT high pulse width                       | toep    | 5   |     | 5   |     | 5   |     | ns                                       |       |

| DT high hold time from CAS high           | toehc   | 5   |     | 5   |     | 5   |     | ns                                       |       |

| OE to high set-up time                    | tосн    | 5   |     | 5   |     | 5   |     | ns                                       |       |

#### **NOTES**

- An initial pause of 200us is required after power-up followed by any 8 RAS, 8 SC cycles before proper device operation is achieved. (DT/OE = High) If the internal refresh counter is used, a minimum of 8 CAS-before-RAS initialization cycles are required instead of 8 RAS cycles.

- 2. VIH (min) and VIL (max) are reference levels for measuring timing of input signals. Transition times are measured between VIH (min) and VIL (max), and are assumed to be 2ns for all input signals.

- Input signal transition from 0V to 3V for AC timing.

- RAM port outputs are measured with a load equivalent to 1 TTL load and 50pF.

- DOUT comparator level: VoH/VoL = 2.0V / 0.8V.

- 4. SAM port outputs are measured with a load equivalent to 1 TTL load and 30pF.

- DOUT comparator level: VoH/VoL = 2.0V / 0.8V.

- 5. Operation within the tRCD (max) limit insures that tRAC (max) can be met. The tRCD (max) is specified as a reference point only: If tRCD is greater than the specified tRCD (max) limit, then access time is controlled exclusively by tCAC.

- 6. Assumes that tRCD ≥ tRCD (max).

- This parameters define the time at which the output achieves the open circuit condition and are not referenced to VOH or VOI

- 8. twcs, tRwb, tcwb, tcpwb and tawb are nonrestrictive operating parameters. They are included in the data sheet as electrical characteristics only. If twcs ≥ twcs (min) the cycle is an early write cycle and the data out pin will remain high impedance for the duration of the cycle. If tcwb ≥ tcwb(min), tRwb ≥ tRwb(min), tcpwb ≥ tcpwb(min), and tawb ≥ tawb(min), then the cycle is a read-write cycle and the data output will contain the data read from the selected address. If neither of the above conditions are satisfied, the condition of the data out is indeterminate.

#### **NOTES**

- 9. Either tRCH or tRRH must be satisfied for a read cycle.

- These parameters are referenced to the CAS leading edge in early write cycles and to the WE leading edge in read-write cycles.

- 11. Operation within the tRAD (max) limit insured that tRAC (max) can be met. tRAD (max) is specified as a reference point only. If tRAD is greater than the specified tRAD (max) limit, then access time is controlled by tAA.

- 12. Power must be applied to the RAS and DT/OE input signal to pull them high before or at the same time as the Vcc supply is turned on.

After power-up, initial status of chip is described below.

| Pin or Register     | Status       |  |  |  |  |

|---------------------|--------------|--|--|--|--|

| QSF                 | Hi-Z         |  |  |  |  |

| Color Register      | Don t Care   |  |  |  |  |

| Write Mask Register | Don t Care   |  |  |  |  |

| Tap Pointer         | Invalid      |  |  |  |  |

| Stop Register       | Default Case |  |  |  |  |

| Wi/DQi              | Hi-Z         |  |  |  |  |

| SAM Port            | Hi-Z         |  |  |  |  |

| SQi                 | Hi-Z         |  |  |  |  |

13. Recommended operating input condition:

Input pulse levels are from 0.0V to 3.0Volts.

All timing measurements are referenced from VIL (max) and VIH (min) with transition time = 2ns

- 14. Assume tT = 3ns.

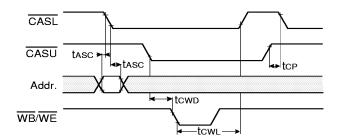

- 15. tasc, tcah are referenced to the earlier CAS falling edge

- 16. tcp is specified from the last  $\overline{\text{CAS}}$  rising edge in the previous cycle to the first  $\overline{\text{CAS}}$  falling edge in the next cycle.

- 17. tcwp is referenced to the later CAS falling edge at word read-modify-write cycle.

- tcwL is specified from WB/WE falling edge to the earlier CAS rising edge.

- 19. tcsn is referenced to earlier CAS falling low before RAS transition low.

- 20. tchr is referenced to the later  $\overline{\text{CAS}}$  rising high after  $\overline{\text{RAS}}$  transition low.

- 21. tasc ≥ tcp(min), at Normal cycle, Assum tr=2.0ns

- 22. tasc < tcp (min), at Normal cycle or any condition at Block write cycle, Assume tT=2ns

### **DEVICE OPERATIONS**

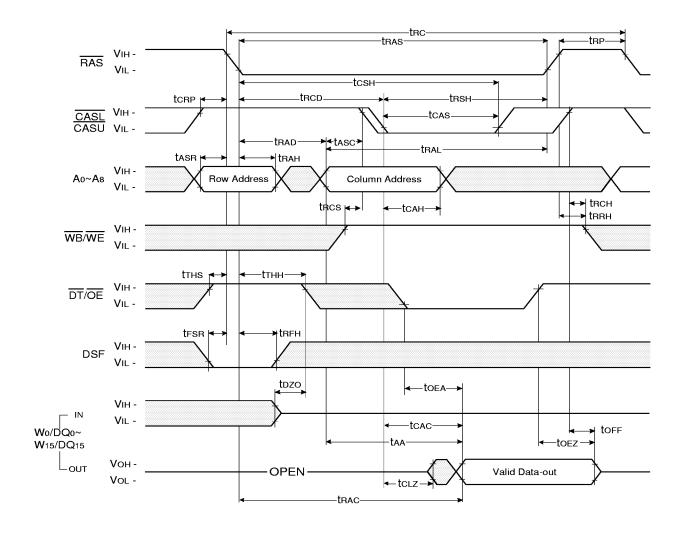

The KM4216C258 contains 4,194,304 memory locations. Eighteen address bits are required to address a particular 16 bit word in the memory array. Since the KM4216C258 has only 9 address input pins, time multiplexed addressing is used to input 9 row and 9 column addresses. The multiplexing is controlled by the timing relationship between the row address strobe (RAS), the column address strobe (CAS) and the valid row and column address inputs.

Operation of the KM4216C258 begins by strobing in a valid row address with RAS while CAS remains high. Then the address on the 9 address input pins are changed from a row address to a column address, and are strobed by CAS.

This is the beginning of any KM4216C/V256 cycle in which a memory location is accessed. The specific type of cycle is determined by the state of the write enable pin and various timing relationship. The cycle is terminated when both RAS and CAS have returned to the high state. Another cycle can be initiated after RAS remains high long enough to satisfy the RAS precharge time(tRP) requirement.

### RAS and CAS Timing

The minimum RAS and CAS pulse widths are specified by tRAS(min) and tcAS(min) respectively. These minimum pulse widths must be satisfied for proper device operation and data integrity. Once a cycle is initiated by bringing RAS low, it must not be aborted prior to satisfying the minimum RAS and CAS pulse widths. In addition, a new cycle must not begin until the minimum RAS precharge time, tRP, has been satisfied. Once a cycle begins, internal clocks and other circuits within the KM4216C258 begin a complex sequence of events. If the sequence is broken by violating minimum timing requirement, loss of data integrity can occur.

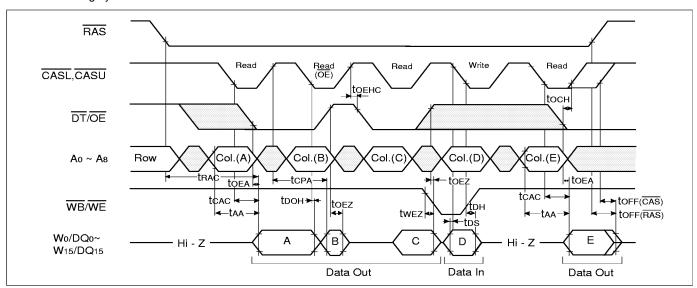

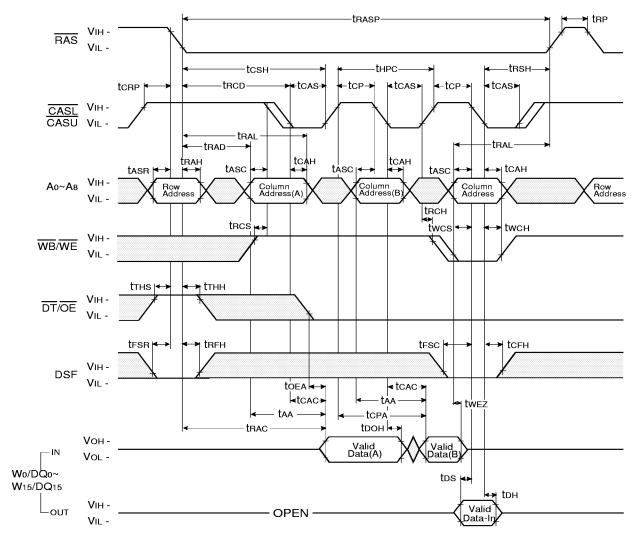

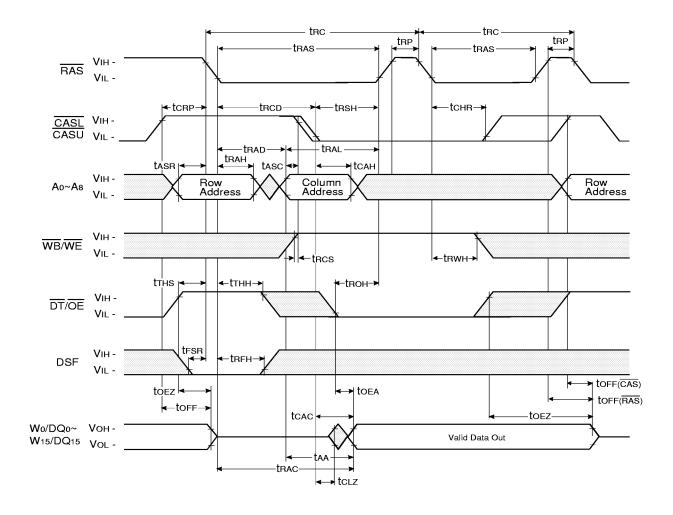

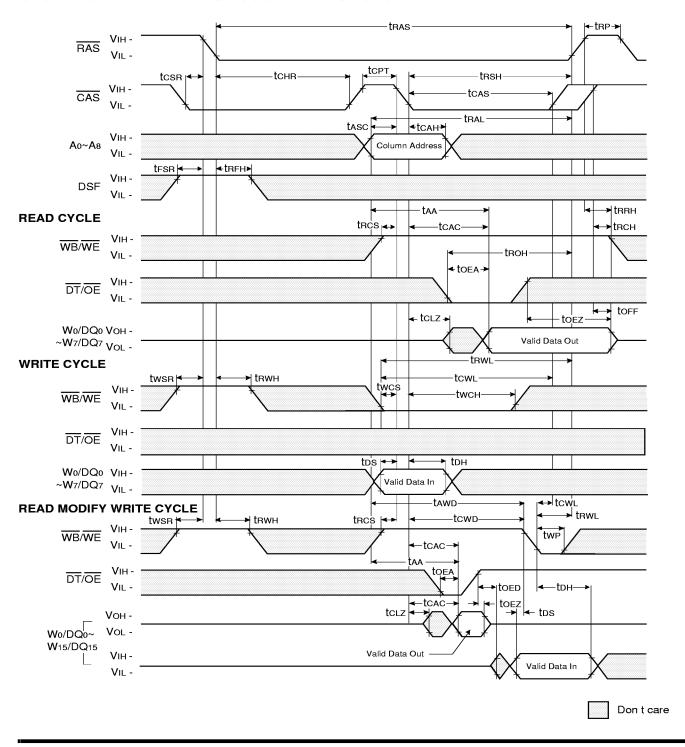

#### **RAM Read**

A RAM read cycle is achieved by maintaining  $\overline{\text{WB/WE}}$  high during a  $\overline{\text{RAS}}$  /  $\overline{\text{CAS}}$  cycle. The access time is normally specified with respect to the falling edge of  $\overline{\text{RAS}}$ . But the access time also depends on the falling edge of  $\overline{\text{CAS}}$  and on the valid column address transition.

If  $\overline{\text{CAS}}$  goes low before tRCD(max) and if the column address is valid before tRAD (max) then the access time to valid data is specified by tRAC. However, If  $\overline{\text{CAS}}$  goes low after tRCD(max) or the column address becomes valid after tRAD(max), access is specified by tCAC or tAA.

The KM4216C258 has common data I/O pins. The  $\overline{DT/OE}$  has been provided so the output buffer  $\underline{\operatorname{can}}$  be precisely controlled. For data to appear at the outputs,  $\overline{DT/OE}$  must be low for the period of time defined by toea.

#### **Extended Data Out**

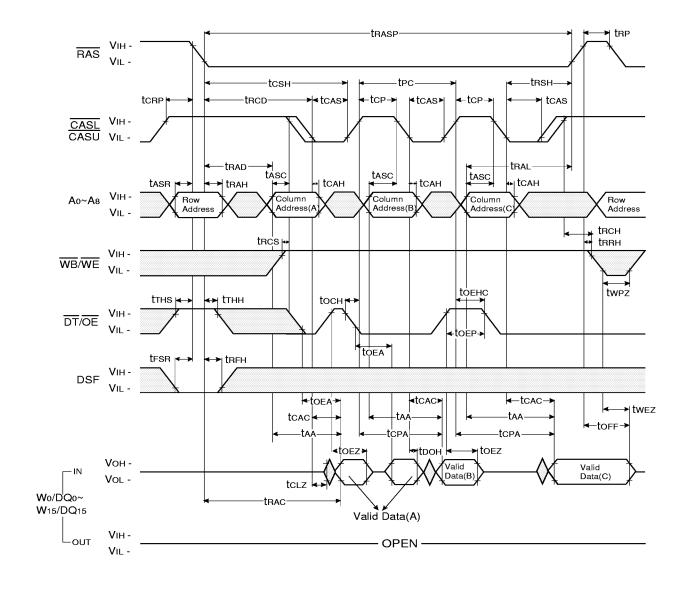

In the conventional RAM Read cycle, Dout buffer is designed to make turn-off by the rising edge of  $\overline{CAS}$ . the KM4216C258 offers an accelerated Fast Page Mode cycle by eliminating output disable from  $\overline{CAS}$  high. This is called "Extended Data Output (or Hyper Page) mode". Data outputs are disabled at  $\overline{WB/WE} = Low, \overline{DT/OE} = High and toff time after RAS and <math display="inline">\overline{CAS}$  are high The toff time is referenced from rising edge of RAS or  $\overline{CAS}$ , whichever occurs later (see Figure 1). What the output buffer is disabling during  $\overline{DT/OE} = high$  is to use bank selection in the frame buffer memory using common I/O line, Read, Write and Read-modify-write cycles are available during the extended data out mode.

Figure 1. Extended Data Output Example

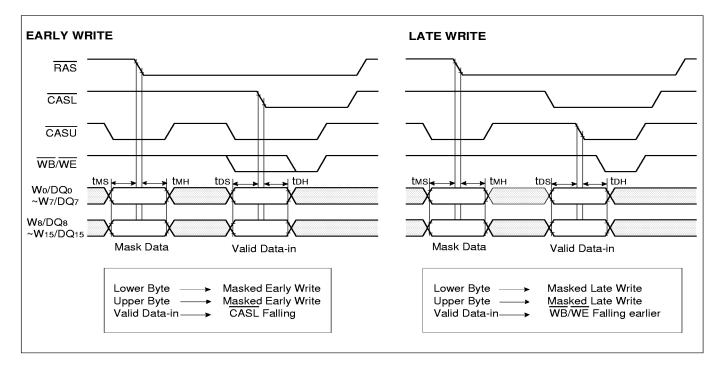

# 2 CAS Byte/Word Read/ Write Operation

The KM4216C258 has 2 CAS control pin, CASL and CASU, and offers asynchronous Read/Write operation with lower byte (Wo/DQo ~ W7/DQ7) and upper byte (W8/DQ8 ~ W15/DQ15). This is called 2CAS Byte/Word Read/Write operation. This operation can be performed in any RAM Read in RAM Write, Block Write, Load Mask Register, and Load Color Register.

### New Masked Write Per Bit

The New Masked Write per Bit cycle is achieved by maintaining CAS high and WB/WE and DSF low at the falling edge of RAS. The mask data on the Wo/DQ0 ~ W15/DQ15 pins are latched into the write mask register at the falling edge of RAS. When the mask data is low, writing is inhibited into the RAM and the mask data is high, data is written into the RAM. The mask data is valid for only one cycle. Mask Data must be provided in every write cycle that a masking operation is desired.

The Early Write cycle is achieved by  $\overline{\text{WB}/\text{WE}}$  low before  $\overline{\text{CAS}}$  falling and the Late Write cycle is achieved by  $\overline{\text{WB}/\text{WE}}$  low after  $\overline{\text{CAS}}$  falling. During the Early or Late Write cycle, input data through  $\overline{\text{Wo}/\text{DQ}_0} \sim \overline{\text{W15}/\text{DQ}_{15}}$  must keep the set-up and hold time at the falling edge of  $\overline{\text{CAS}}$  or  $\overline{\text{WB}/\text{WE}}$ .

If WB/WE is high at the falling edge of RAS, no masking operation is performed (see Figure 2.3).

And if  $\overline{\text{CASL}}$  is high during  $\overline{\text{WB}/\text{WE}}$  low, write operation of lower byte does not perform and if  $\overline{\text{CASU}}$  is high, also write operation of upper byte does not execute.

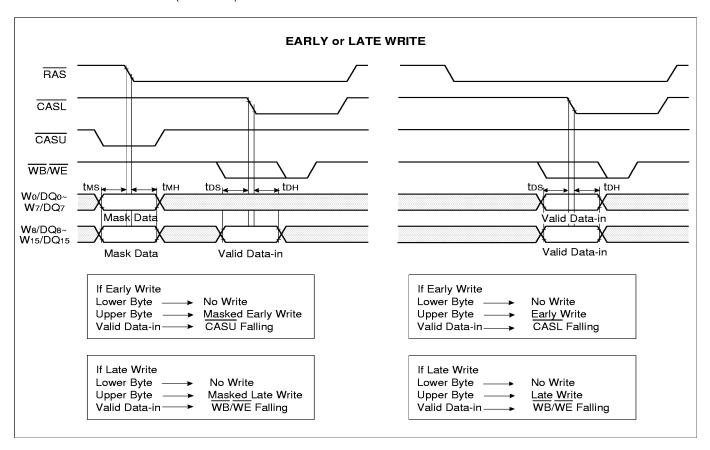

#### Load Mask Register (LMR)

The Load Mask Register operation loads the data present on the Wi/DQi pins into the Mask Data Register at the falling edge of CAS or WB/WE. The LMR cycle is performed if DSF high, WB/WE high at the RAS falling edge and DSF low at the CAS falling edge. If an LMR is done, the KM4216C258 are set to Old masked write mode.

#### Old Masked Write Per Bit

This mode is enabled through the Load Mask Register (LMR) cycle. If an LMR is done, all Masked Write are Old masked Write Per Bit and the I/O mask data will be provided by the Mask Data Register (see Figure 4).

The mask data is applied in the same manner as in New Masked Write Per Bit mode. Mask Data Register's content is changed by the another LMR, To reset the device back to the New Masked Write Mode, CBRR(CBR Refresh with option reset) cycle must be performed. After power-up, the KM4216C258 initializes in the New Masked Write Mode.

Figure 2. Byte Write and New Masked Write Cycle Example1. (Early Write & Late Write)

Figure 3. Byte Write and New Masked Write Cycle Example2.

### **Fast Page Mode**

The KM4216C258 has Fast Page Mode capability provides high speed read, write or read-modify-write access to all memory locations within a selected row. In this cycle, read, write, read-modify-write, and block write cycles can be mixed in any order. In one RAS cycle, 512 word memory cells of the same row address can be accessed. While RAS is held low to maintain the row address, CAS is cycled to strobe in additional column addresses. This eliminates the time required to set up and strobe sequential row addresses for the same page.

### Load Color Register (LCR)

A Load Color Register cycle is performed by keeping DSF high on the both the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ . Color data is loaded on the falling edge of  $\overline{CAS}$  (early write) or  $\overline{WE}$  (late write) via the Wo/DQ0 ~ W7/DQ7 (lower byte), W8/DQ8 ~ W15/DQ15 (upper byte) pins. This data is used in Block Write cycles and remains unchanged until the next Load Color Register cycle.

Figure 4. New Masked Write Cycle and Old Masked Write Cycle Example

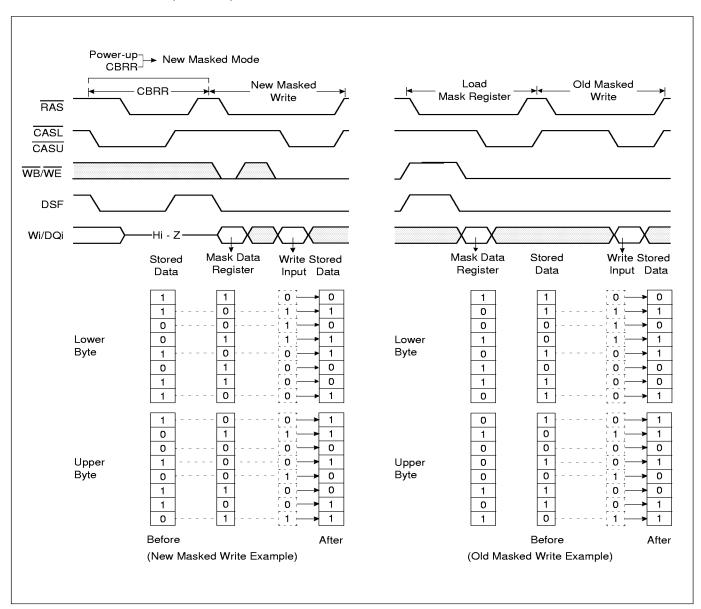

#### **Block Write**

In a Block Write cycle 8 adjacent column locations can be written simultaneously with the same data, resulting in fast screen fills of the same color.

First, the internal 16 bit Color Register must be loaded with the data to be written by performing a Load Color Register(LCR) cycle.

When a Block write cycle is performed, each bit of the Color

Register is written into 8 adjacent locations of the same row of each corresponding bit plane(16). This results in a total of 128bits being written in a single Block Write cycle compared to 16-bits in a normal Write cycle.

The Block Write cycle is performed if DSF is low at the falling edge of the RAS and high at the falling edge of CAS.

Figure 5. Block Write Scheme

**Address Lines**: The row address is latched on the falling edge of  $\overline{RAS}$ . Since 8 columns are being written at a time, the minimum increment required for the column address is eight.

Therefore, when the column address is latched at the falling edge of CAS, the 3 LSBs,  $A_0 \sim A_2$  are ignored and only bits( $A_3 \sim A_8$ ) are used to define the location of the first bit out of the eight to be written.

**Data Lines**: On the falling edge of  $\overline{CAS}$ , the data on the Wo/DQo ~ W15/DQ15 pins provide column mask data. That is, for each of the eight bits in all 16-bit planes, writing of Color Register contents can be inhibited. For example, If Wo/DQo = 1 and W1/DQ1 = 0, then the Color Register contents will be written into the first bit out of the 8, but the second remains unchanged.

Fig. 5 shows the correspondence of each data line to the column mask bits.

A masked Block Write cycle identical to a New/Old Masked Write-per-bit cycle except that each of the 16-bit planes being masked is operating on 8 column locations instead of one.

To perform a Masked Block Write cycle, both DSF and WB/WE must be low at the falling edge of  $\overline{RAS}$ . DSF must be high at the falling edge of  $\overline{CAS}$ . In new mask mode, Mask data is latched into the device via the Wo/DQo ~ W15/DQ15 pins at the falling edge of  $\overline{RAS}$  and needs to be re-entered for every new  $\overline{RAS}$  cycle. And  $\overline{WB/WE}$  must be low, DSF must be high on the falling edge of  $\overline{CAS}$ . In Old Mask Mode, I/O mask data will be provided by the Mask Data Register.

Figure 6. Block Write Example and Timing

#### **Data Output**

The KM4216C258 has three state output buffer controlled by DT/OE and CAS/RAS. If DT/OE is high when CAS and RAS low, the output state is high impedance (High-z). In any cycle, the output goes low impedance state after tclz of the first CAS falling edge. Invalid data may be present at the output during the time after tclz and the valid data appears at the output. The timing parameter trac, tcac and tax specify when the valid data will be present at the output.

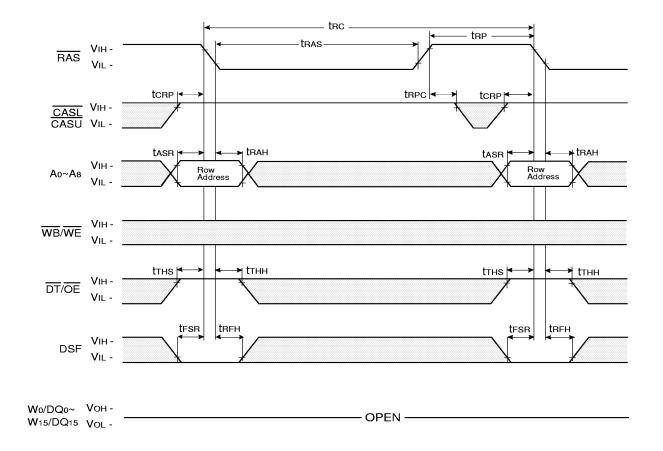

#### Refresh

The data in the KM4216C258 is stored on a tiny capacitor within each memory cell. Due to leakage the data may leak off after a period of time. To maintain data integrity it is necessary to refresh each of the 512 rows every 8 ms. Any operation cycle performed in the RAM port refreshes the 8192 bits selected by the row addresses or an on-chip refresh address counter. Either a burst refresh or distributed refresh may be used. There are several ways to accomplish this.

#### RAS-Only Refresh

This is the most common method for performing refresh. it is performed by strobing in a row address with  $\overline{RAS}$  while  $\overline{CAS}$  remains high. This cycle must be repeated for each of the 512 row address, (A0 ~ A8).

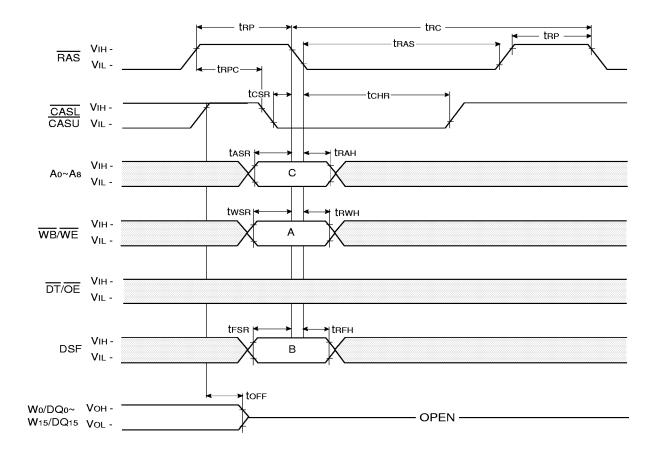

#### CAS-Before-RAS Refresh

The KM4216C258 has  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  on chip refresh capability that eliminates the need for external refresh address. If  $\overline{\text{CAS}}$  is held low for the specified set up time(tcsr) before  $\overline{\text{RAS}}$  goes low, the on chip refresh circuitry is enabled.

An internal refresh operation occurs automatically. The refresh address is supplied by the on chip refresh address counter which is then internally incremented in preparation for the next CAS-before-RAS refresh cycle.

The KM4216C258 has 3 type CAS-before-RAS refresh operations CBRR, CBRN, CBRS

CBRR (CBR Refresh with option reset) is set if DSF low at the RAS falling edge. This mode initiates to change from old masked write to new masked write cycle, and reset stop register to default values.

CBRN (CBR refresh without reset) is set if DSF high when  $\overline{\text{WB}}/\overline{\text{WE}}$  is high at the falling edge of  $\overline{\text{RAS}}$  and simply does only refresh operation.

CBRS (CBR Refresh with stop register set) cycle is set if DSF high when  $\overline{WB/WE}$  is low and this mode is to set stop register s value.

#### Hidden Refresh:

A hidden refresh cycle may be performed while maintaining the latest valid data at the output by extending the CAS active time and cycling RAS. The KM4216C258 hidden refresh cycle is actually a CAS-before-RAS refresh cycle within an extended read cycle.

The refresh row address is provided by the on-chip refresh address counter.

#### Other Refresh Methods:

It is also possible to refresh the KM4216C258 by using read, write or read-modify-write cycles. Whenever a row is accessed, all the cells in that row are automatically refreshed. There are certain applications in which it might be advantageous to perform refresh in this manner but in general RAS-only or CAS-before-RAS refresh is the preferred method.

Table.1 Truth Table for Transfer Operation

\* : Don t care

| RAS Falling Edge |       |       | Function | Transfer | Transfer            |                  |          |

|------------------|-------|-------|----------|----------|---------------------|------------------|----------|

| CAS              | DT/OE | WB/WE | DSF      | SE       | i diletion          | Direction        | Data Bit |

| Н                | L     | Н     | L        | *        | Read Transfer       | RAM→ SAM         | 512 x 16 |

| Н                | L     | Н     | Н        | *        | Split Read Transfer | RAM <i>→</i> SAM | 256 x 16 |

#### **Transfer Operation**

Transfer operation is initiated when  $\overline{\text{DT}/\text{OE}}$  is low at the falling edge of  $\overline{\text{RAS}}$ . The state of DSF when  $\overline{\text{RAS}}$  goes low is used to select between normal transfer and split transfer cycle. Each of the transfer cycle is described in the truth table for transfer operation (Table 1).

#### Read Transfer (RT)

The Read Transfer operation is set if  $\overline{\text{DT}/\text{OE}}$  is low,  $\overline{\text{WB}/\text{WE}}$  is high and DSF low at the falling edge of RAS. The row address bits in the read transfer cycle indicate which sixteen 512bit DRAM row portions are transferred to the sixteen SAM data register portions. The column address bits indicate the start address of the SAM Registers when SAM data read operation is performed. If MSB of column address is low during Read transfer operation, the QSF state will be set low level and this indicates the start address of SAM register is present at lower half of SAM port. (If As is high, QSF will be high and means the start address is in upper half) Read Transfer may be accomplished in two ways. If the transfer is to be synchronized with the SC. DT/OE is taken high after CAS goes low. This is usually called "Real Time Read Transfer". Note that the rising edge of DT/OE must be synchronized with the rising edge of SC(tTSL/tTSD) to retain the continuity of serial read data output. If the transfer does not have to be synchronized with SC, DT/OE may go high before CAS goes low and the actual data transfer will be timed internally.

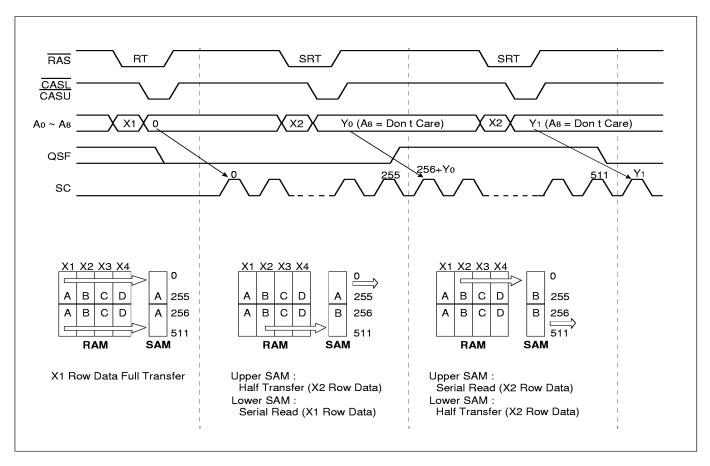

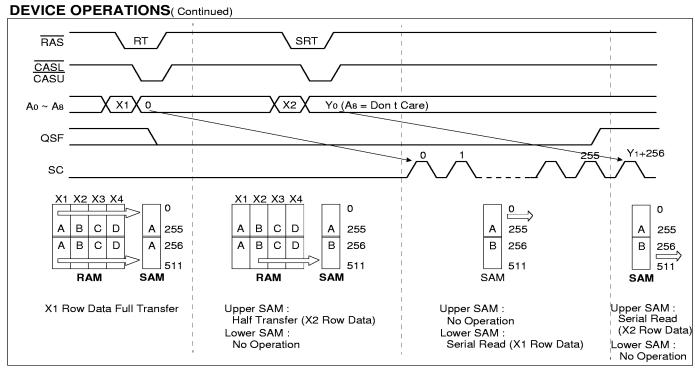

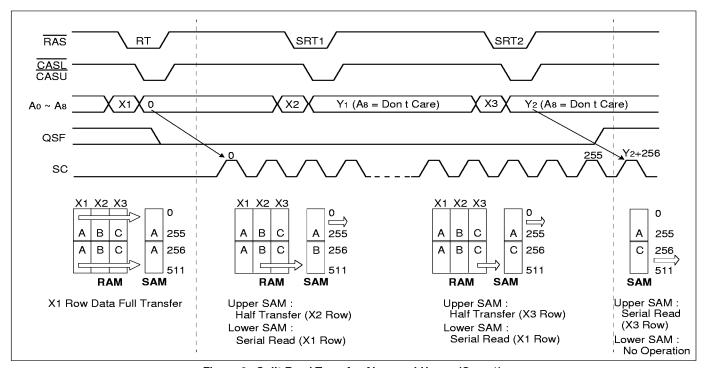

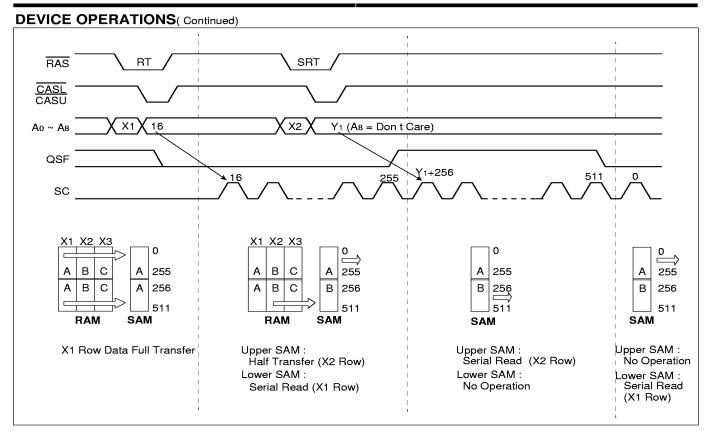

#### Split Read Transfer (SRT)

In a graphic system, if data has to be transferred from DRAM to SAM while in the middle of a display line, the only way to do this seamlessly is performed by a Real Time Read Transfer cycle. However, this cycle has many critical timing restriction (between SC,  $\overline{\text{DT}/\text{OE}}$ ,  $\overline{\text{RAS}}$  and  $\overline{\overline{\text{CAS}}}$ ) because the transfer has to occur at the first rising edge of  $\overline{\text{DT}/\text{OE}}$

The split read transfer(SRT) cycle eliminates the need for this critical transfer timing, thereby simplifying system design. This is accomplished by dividing the SAM port into 2 halves of 256 bits each. A Split Read Transfer loads only the lower or upper half. While data is being serially read from one half of the SAM Register, new RAM data can be transferred to the other half. Since transfer timing is controlled internally, there is no timing restriction between  $\overline{\text{DT}/\text{OE}}$  and  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ , SC.

A normal Read Transfer cycle must be executed before performing a Split Read Transfer to set the state of QSF. A Split Read Transfer cycle is initiated by keeping DSF and WB/WE high and DT/OE low at the falling edge of RAS.

Address: The row address is latched on the falling edge of RAS. The column address defined by (A0 ~ A7) defines the starting address of the SAM port from which data will begin shifting out. Column address pin A8 is a "Don t Care."

The QSF pin indicates which SAM half is shifting out serial data (0 = Lower, 1 = Upper). A Split Read Transfer will load data into the other half. The state of the QSF output changes when the SAM address counter reaches a split SAM boundary (e.g. 255th or 511th bit).

Examples of SRT application are shown in Fig. 7 through Fig.10.

The normal usage of Split Read Transfer cycle is described in Fig.7. When Read Transfer is executed, data from X1 row address is fully transferred to the SAM port and serial Read is started from 0 (Tap address).

If SRT is performed while data is being serially read from lower half SAM, data from X2 row address is transferred to upper half SAM. The Tap address of SRT is loaded after the boundary location of lower half SAM (255th SC) is accessed and the QSF state is changed into high level at the rising edge of 255th SC. Note that in this case "256+Y0" Tap address instead of "Y0" is loaded.

The another example of SRT cycle is described in Fig.8.

When Serial Read is performed after executing RT and SRT in succession, the data accessed by first SC is the starting address given by RT Tap address. Serial data access from the starting address given by SRT cycle is performed after the data of RT to lower boundary (255th SC) is completed. Fig. 9 and 10 are the example of abnormal SRT cycle.

If SRT1 and SRT2 are performed in succession before accessing the boundary like Fig. 9, the data transferred by SRT2 overwrites the data transferred by SRT1, so that data followed by SRT2 will be remain in the upper half SAM. The Serial Read after lower boundary 255th SC is started from the starting address given by SRT2 cycle. The Fig. 10 indicates that SRT cycle is not performed until Serial Read is completed to the boundary location 511.

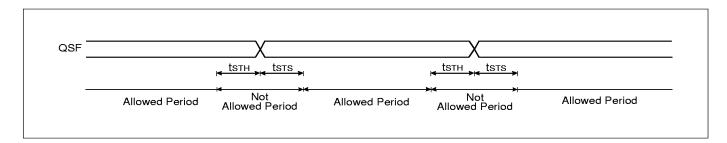

In this case, the internal serial counter is designed to designate "0" address after boundary 511, therefore accessed data from 0 address corresponds to the old data transferred by RT. Note that there is not allowed period of SRT cycle. Since a SRT cycle must be ended before tsth and started after tsts, a split transfer is not allowed during tsth + tsts (see Fig. 11)

A Split Read Transfer does not change the direction of the SAM I/O port.

Figure 7. Split Read Transfer Normal Usage

Figure 8. Split Read Transfer Normal Usage

Figure 9. Split Read Transfer Abnormal Usage (Case 1)

Figure 10. Split Read Transfer Abnormal Usage (Case 2)

Figure 11. Split Transfer Cycle Limitation Period

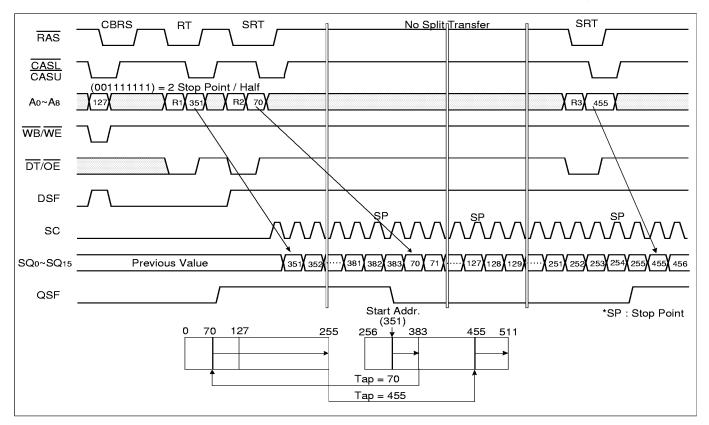

#### Programmable Split SAM

In split SAM mode, SAM is divided into the lower half and the upper half, After the last address of each half SAM (255 or 511) is accessed, the access will be changed one half of the SAM to the other half (at the loaded Tap address). This last address is called stop point.

The KM4216C258 offers user-programmable Stop Points. The Stop Points and size of the resulting partitions are shown in Table 2. The Stop Point is set by performing CBRS cycle. The CBRS cycle s condition is  $\overline{\text{WB/WE}}$  low, DSF high at the falling edge of  $\overline{\text{RAS}}$  in CBR cycle and the Stop Point is determined by row address entering at this time.

The Stop Point will not become valid until a SRT cycle is done. The Stop Point does not effect to SAM in normal RT, RRT cycle. In Figure 12. programmable split SAM operation is shown. if a SRT cycle was done before the partition boundary (383), the access will jump to the TAP address (70) of the next half. Otherwise, the access will continue in the same half until a SRT occurs at the SAM half boundary (255, 511). Note that the Stop Point may be changed at any time by performing another CBRS, and New Stop Point will not be valid until a SRT is performed.

To reset Stop Point, CBRR cycle must be performed. CBRR is a CBR cycle with DSF low at the falling edge of  $\overline{\text{RAS}}$  The CBRR will take effect immediately; it does not require a SRT to become active valid.

**Table. 2 Stop Point Setting Address**

| Stop Register = Store The Address of Serial Access Use on the Split Transfer Cycle Stop Pointer Set → CBRS Cycle |                           |            |            |            |            |            |       |  |

|------------------------------------------------------------------------------------------------------------------|---------------------------|------------|------------|------------|------------|------------|-------|--|

| Number                                                                                                           | Stop Form Sotting Address |            |            |            |            |            | ess   |  |

| Stop Points<br>/Half                                                                                             | Faitition                 | <b>A</b> 8 | <b>A</b> 7 | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | Аз∼Ао |  |

| 1                                                                                                                | (1x256)x2                 | ×          | 1          | 1          | 1          | 1          | ×     |  |

| 2                                                                                                                | (2x128)x2                 | х          | 0          | 1          | 1          | 1          | х     |  |

| 4                                                                                                                | (4x64)x2                  | Х          | 0          | 0          | 1          | 1          | х     |  |

| 8                                                                                                                | (8x32)x2                  | Х          | 0          | 0          | 0          | 1          | ×     |  |

| 16                                                                                                               | (16x16)x2                 | Х          | 0          | 0          | 0          | 0          | Х     |  |

\*Other Case = Inhibit, X =don t care.

Figure 12. Programmable Split SAM Operation

### **TIMING DIAGRAMS**

**READ CYCLE**

Don t care

# **FAST PAGE MODE READ CYCLE (Extended Data Out)**

Don t care

# TURTH TABLE FOR WRITE CYCLE (1)

|                              | RAS                |           |                                           | CAS       | CAS or WB/WE      |

|------------------------------|--------------------|-----------|-------------------------------------------|-----------|-------------------|

| FUNCTION                     | <u>*1</u><br>WB/WE | *2<br>DSF | *3<br>Wi/DQi <sub>(4)</sub><br>(New Mask) | *4<br>DSF | *5<br>Wi/DQi      |

| Normal Write                 | 1                  | 0         | X                                         | 0         | Write Data        |

| Masked Write                 | 0                  | 0         | Write Mask                                | 0         | Masked Write Data |

| Block Write (No I/O Mask)(4) | 1                  | 0         | X                                         | 1         | Column Mask       |

| Masked Block Write(4)        | 0                  | 0         | Write Mask                                | 1         | Column Mask       |

| Load Mask Data Register(2)   | 1                  | 1         | X                                         | 0         | Write Mask Data   |

| Load Color Register          | 1                  | 1         | X                                         | 1         | Color Data        |

#### Note:

- 1) Reference truth table to determine the input signal states of \*1, \*2, \*3, \*4, and \*5 for the write cycle timing diagram, on the following page.

- 2) Old Mask data load

- 3) Function table for Old Mask and New Mask

| IF                |     | *1    | *3                                                                           | Note                                              |  |  |

|-------------------|-----|-------|------------------------------------------------------------------------------|---------------------------------------------------|--|--|

|                   |     | WB/WE | Wi/DQi                                                                       |                                                   |  |  |

|                   | YES | 0     | х                                                                            | Write using mask register data<br>(Old Mask Data) |  |  |

| LMR               |     | 1     | х                                                                            | Non Masked Write                                  |  |  |

| Cycle<br>Executed | NO  | 0     | Write using New Mask Data  Mask Wi/DQi=0 Write Disable Wi/DQi=1 Write Enable |                                                   |  |  |

|                   |     | 1     | Х                                                                            | Non Masked Write                                  |  |  |

X : Don t care

4) Function Table for Block Write Column Mask

| Column<br>Address |    |    |  |  |  |  |

|-------------------|----|----|--|--|--|--|

| <b>A</b> 2        | Αı | Ao |  |  |  |  |

| 0                 | 0  | 0  |  |  |  |  |

| 0                 | 0  | 1  |  |  |  |  |

| 0                 | 1  | 0  |  |  |  |  |

| 0                 | 1  | 1  |  |  |  |  |

| 1                 | 0  | 0  |  |  |  |  |

| 1                 | 0  | 1  |  |  |  |  |

| 1                 | 1  | 0  |  |  |  |  |

| 1                 | 1  | 1  |  |  |  |  |

| *              | 5                | IF            |                      |  |  |

|----------------|------------------|---------------|----------------------|--|--|

| Lower Byte     | Upper Byte       | Wi/DQi=0      | Wi/DQi=1             |  |  |

| <b>W</b> o/DQo | W8/DQ8           |               |                      |  |  |

| <b>W</b> 1/DQ1 | <b>W</b> 9/DQ9   |               |                      |  |  |

| W2/DQ2         | <b>W</b> 10/DQ10 |               | Color Register Data  |  |  |

| W3/DQ3         | <b>W</b> 11/DQ11 | No Change the | is Written to the    |  |  |

| <b>W</b> 4/DQ4 | <b>W</b> 12/DQ12 | Internal Data | Corresponding Column |  |  |

| W5/DQ5         | W13/DQ13         |               | Address Location     |  |  |

| W6/DQ6         | <b>W</b> 14/DQ14 |               |                      |  |  |

| <b>W</b> 7/DQ7 | <b>W</b> 15/DQ15 |               |                      |  |  |

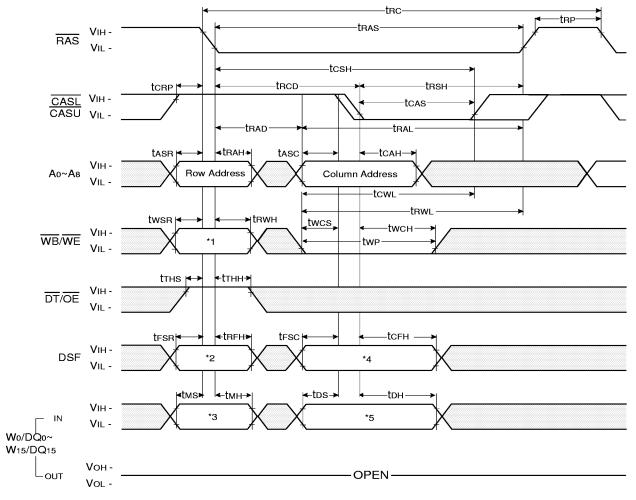

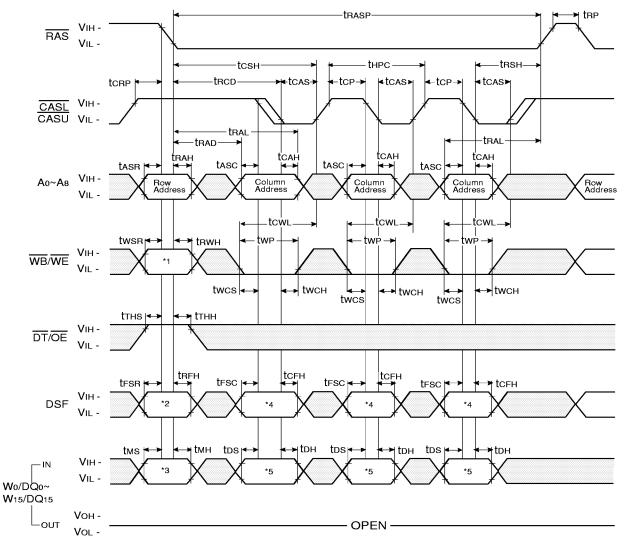

### **EARLY WRITE CYCLE**

Note: In Block Write cycle, only Column Address A3 ~ A8 are used.

Don t care

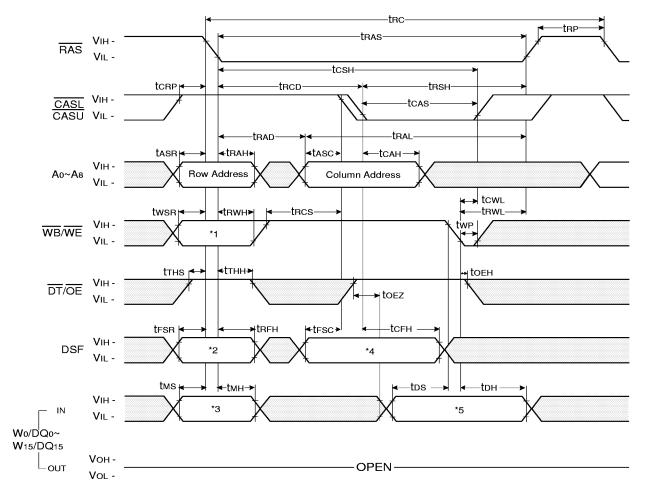

### LATE WRITE CYCLE

Note : In Block Write cycle, only Column Address A3  $\sim$  A8 are used.

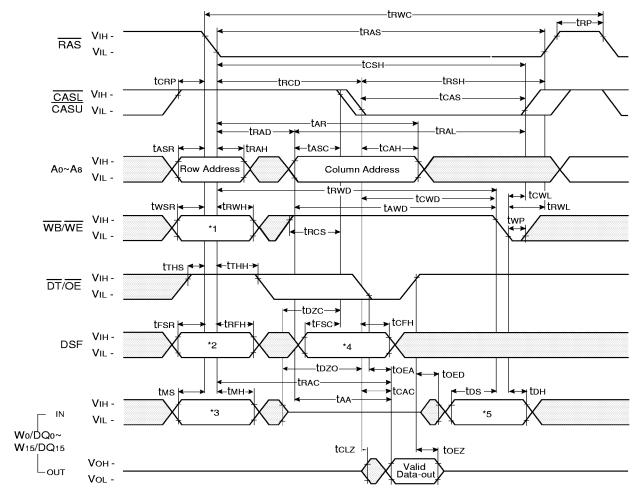

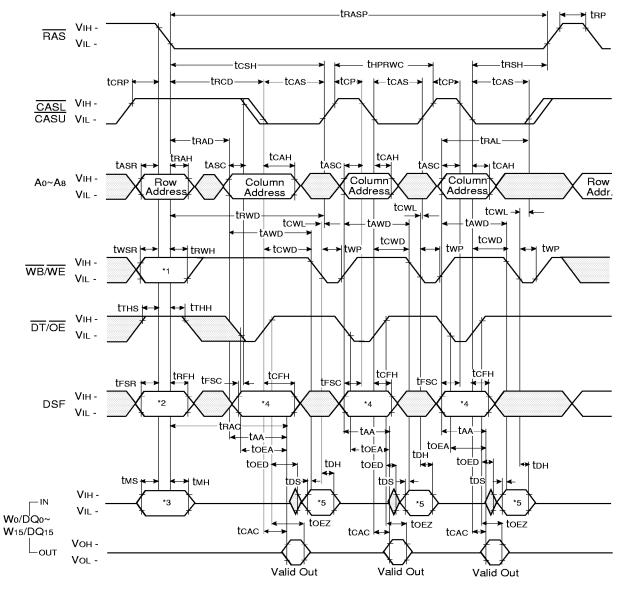

### READ-WRITE/READ-MODIFY-WRITE CYCLE

Note: In Block Write cycle, only Column Address A3 ~ A8 are used.

Don t care

## FAST PAGE MODE READ/WRITE CYCLE (Extended Data Out)

Note : In Block Write cycle, only Column Address A3  $\sim$  A8 are used.

Don t care

### **FAST PAGE MODE EARLY WRITE CYCLE**

Note: In Block Write cycle, only Column Address A3 ~ A8 are used.

Don t care

### FAST PAGE MODE READ-MODIFY-WRITE CYCLE

Note: In Block Write cycle, only Column Address A3 ~ A8 are used.

Don t care

# **RAS-ONLY REFRESH CYCLE**

### **HIDDEN REFRESH CYCLE**

Don t care

# CAS-BEFORE-RAS REFRESH CYCLE

CAS-before-RAS Refresh Cycle Function Table

| FUNCTION                                         |      | LOGIC STATES |   |              |  |

|--------------------------------------------------|------|--------------|---|--------------|--|

|                                                  |      | Α            | В | С            |  |

| CAS-before-RAS Refresh Cycle (Reset All Options) | CBRR | Х            | 0 | Х            |  |

| CAS-before-RAS Refresh Cycle (Stop Register Set) | CBRS | 0            | 1 | Stop Address |  |

| CAS-before-RAS Refresh Cycle (No Reset)          | CBRN | 1            | 1 | х            |  |

Don t care

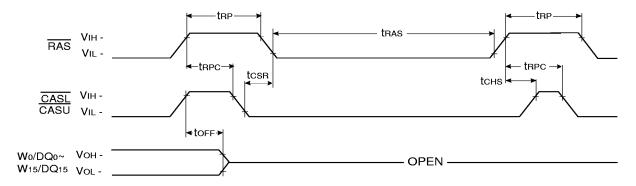

# CAS-BEFORE-RAS SELF REFRESH CYCLE

\* CBR Self Refresh Cycle is Applicable With CBRR, CBRS, or CBRN Cycle

Don t care

## CAS-BEFORE-RAS REFRESH COUNTER TEST CYCLE

Rev. 0.11 (Aug. 1998)

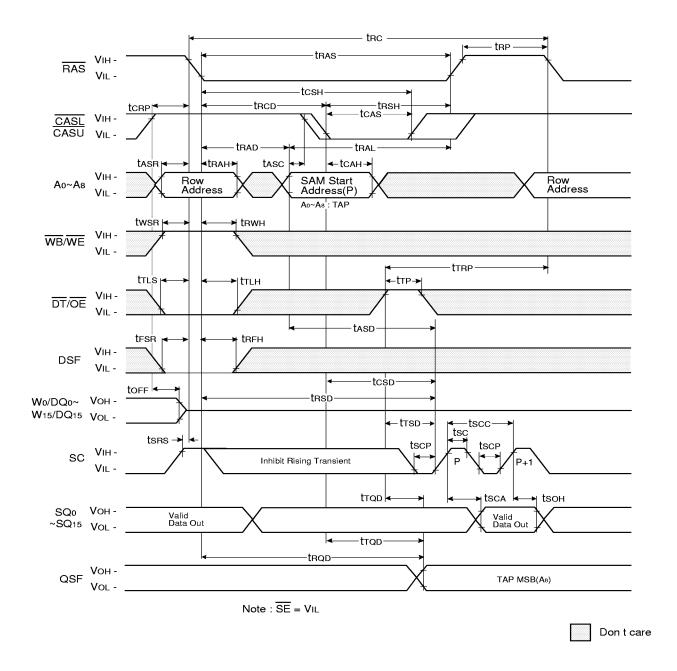

### **READ TRANSFER CYCLE**

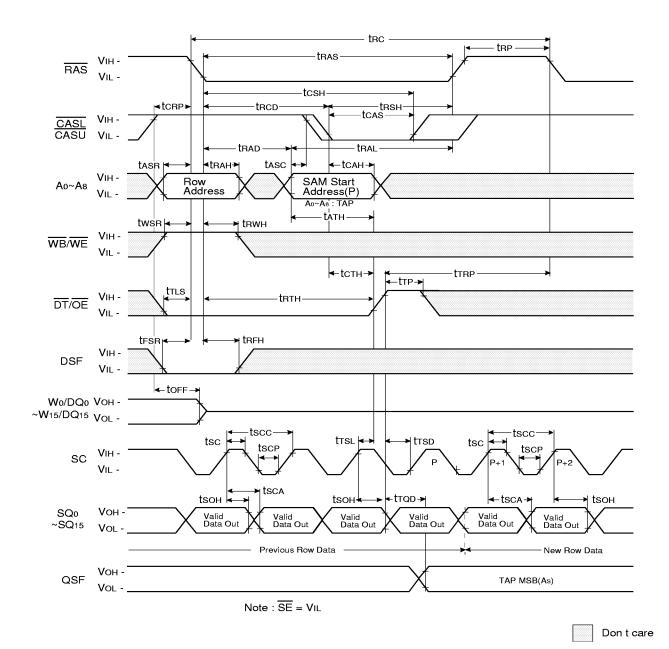

### **REAL TIME READ TRANSFER CYCLE**

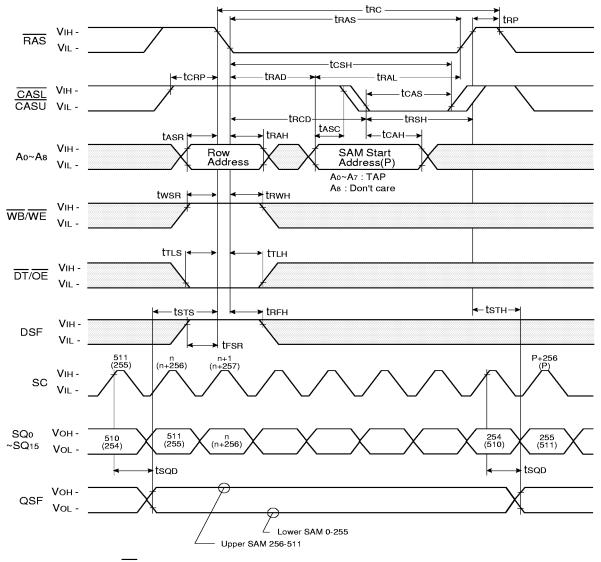

### **SPLIT READ TRANSFER CYCLE**

Note :  $\overline{SE} = V_{IL}$

Don t care

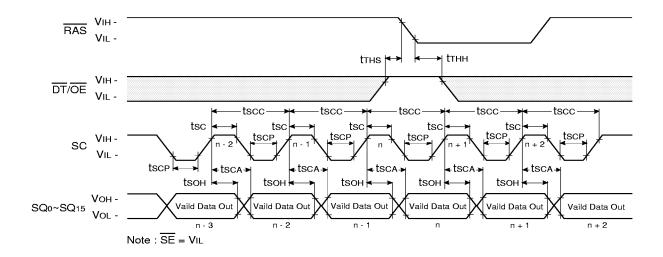

# SERIAL READ CYCLE (SE=VIL)

# SERIAL READ CYCLE (SE Controlled Outputs)

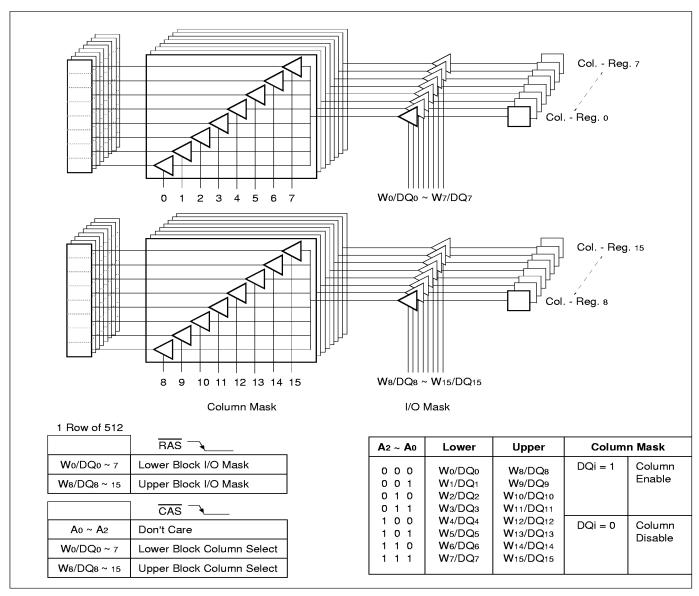

### **PACKAGE DIMENSIONS**

64 Pin Plastic Small Out Line Package (Units : Millimeters)